# Efficient Memory Sharing in the Xen Virtual Machine Monitor

Jacob Faber Kloster Jesper Kristensen Arne Mejlholm

${jk|cableman|mejlholm}@cs.aau.dk$

at

DEPARTMENT OF COMPUTER SCIENCE,

AALBORG UNIVERSITY

JANUARY 2006

## Department of Computer Science

Aalborg University

#### Title:

Efficient Memory Sharing In the Xen Virtual Machine Monitor

#### Semester:

Dat5

2. September 2005 -

10. January, 2006

#### Group:

D515a, 2005-2006

#### Members:

Jacob Faber Kloster Jesper Kristensen Arne Mejlholm

## Supervisor:

Gerd Behrmann

Copies: 5

Report – pages: 80

Appendix – pages: 6

Total pages: 86

## Synopsis:

This report describes the design of an efficient mechanism for sharing memory between virtual machines. The design uses content-based page sharing, which uses a compare-by-hash technique to locate pages eligible for sharing. It uses a fast, low-collision, uniformly distributed hash function called SuperFastHash combined with common hash tables using open addressing. Reducing the number of pages by sharing provides an opportunity for doing overcommitment of memory through a technique called ballooning.

The mechanism will be implemented as a modification to the Xen Virtual Machine Monitor, which is a high performance paravirtualization framework built on top of the Linux kernel.

The background research for the report summarizes important work on virtualization.and memory sharing between virtual machines as well as explaining key concepts of Xen with focus on virtual memory.

**Keywords:** VM, VMM, hypervisor, Xen, virtualizability, paravirtualization, COW, memory sharing, shadow page table, ballooning, overcommitment, hash functions, SFH.

## **Preface**

This first part of our thesis documents our background research on exploring memory sharing in a virtualization setting as well as the design of an extension to a known virtual machine monitor to enable it to do memory sharing.. The report has been developed as part of our DAT5 semester at Department of Computer Science, Aalborg University.

The second part will address the implementation and evaluation of the ideas presented in this part of the thesis.

We would like to thank Michael Vrable for the source code used in the Potemkin framework.

| Jacob Faber Kloster | Jesper Kristensen |

|---------------------|-------------------|

|                     |                   |

|                     |                   |

| Arne Mejlho         | olm               |

## Contents

| Ι | An             | alysis                                    | 7  |

|---|----------------|-------------------------------------------|----|

| 1 | Vir            | tualization                               | 11 |

|   | 1.1            | Motivation for Virtualization             | 11 |

|   | 1.2            | Virtualizability                          | 13 |

|   | 1.3            | Other Approaches to Virtualization        | 14 |

|   | 1.4            | The Legacy                                | 16 |

|   | 1.5            | Application of Virtualization in Research | 17 |

| 2 | Xer            | 1                                         | 19 |

|   | 2.1            | Xen Architecture                          | 20 |

|   | 2.2            | Memory Management                         | 22 |

|   |                | 2.2.1 Memory in Xen                       | 22 |

|   |                | 2.2.2 Linux Page Tables                   | 23 |

|   |                | 2.2.3 Xen Page Tables                     | 25 |

|   |                | 2.2.4 Shadow Page Tables                  | 26 |

|   |                | 2.2.5 Page Faults                         | 28 |

|   |                | 2.2.6 Ballooning                          | 30 |

| 3 | Mo             | tivation and Goals                        | 31 |

|   | 3.1            | Experiments                               | 31 |

|   |                | 3.1.1 Working Set Changes                 | 32 |

|   |                | 3.1.2 Sharing Potential                   | 33 |

|   | 3.2            | Project Goal                              | 33 |

|   | 3.3            | Limitations                               | 34 |

| 4 | $\mathbf{Rel}$ | ated Work                                 | 35 |

|   | 4.1            | Compare-By-Hash                           | 35 |

|   | 4.2            | Copy-On-Write                             | 35 |

|   | 4.3            | Shared Virtual Storage on VM/370          | 36 |

|   | 4.4            | Transparent Page Sharing                  | 37 |

|   | 4.5            | Content Based Page Sharing                | 37 |

|   | 4.6            | Flash Cloning                             | 38 |

|   | 4.7            | Comparison of the Different Approaches    | 38 |

| 5 | Cor            | nclusion                                  | 41 |

| Voll / Vo (FNV)                                                     |  |

|---------------------------------------------------------------------|--|

| $\operatorname{ns}\left(\mathrm{BJ}\right)\ldots\ldots\ldots\ldots$ |  |

| Hash (SFH)                                                          |  |

| sh Functions MD5/SHA1                                               |  |

| 1                                                                   |  |

|                                                                     |  |

| es                                                                  |  |

| y Mapped Trie (HAMT)                                                |  |

| ata Structures                                                      |  |

|                                                                     |  |

|                                                                     |  |

|                                                                     |  |

| ect Sharing                                                         |  |

| inuous Hashing                                                      |  |

|                                                                     |  |

| nt Hypervisor Level                                                 |  |

| r Level                                                             |  |

| Level                                                               |  |

|                                                                     |  |

| s in the Hypervisor Level Design                                    |  |

| s in the Transparent Hypervisor Level                               |  |

| esigns                                                              |  |

|                                                                     |  |

|                                                                     |  |

|                                                                     |  |

# Part I Analysis

## Part Introduction

This part of the report serves as an introduction to the problem area. Briefly stated: Our focus in the project is to address memory sharing between virtual machines in a virtualization environment. However in order to explain the problems in an adequate manner, we will not present a further description of the problem until we have provided the reader with a solid understanding of virtualization (Chapter 1) and the virtualization framework we intend to make use of (Chapter 2). Having established a common understanding we return to the problem in Chapter 3 and explicitly state our goals. Having stated the goals of the project, we compare approaches taken in related work in Chapter 4. Finally in Chapter 5 we will conclude this part of the report.

## Chapter 1

## Virtualization

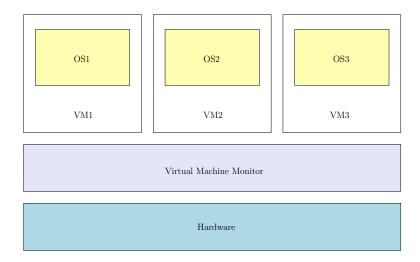

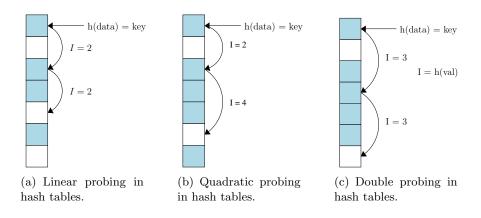

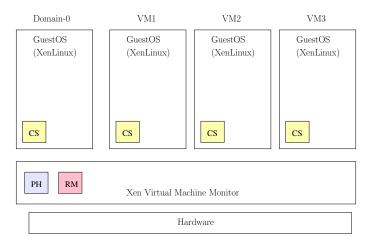

Virtualization is built around two key concepts: A Virtual Machine Monitor (VMM) and a number of Virtual Machines (VMs). The VMM provides an abstraction that makes it possible to run one or more VMs on a single physical machine as pictured in Figure 1.1 on the following page. Traditionally the VMM provides the VM with a virtual interface<sup>1</sup> for each hardware component. The VMM validates accesses to the hardware through these virtual interfaces to ensure isolation between different VMs. Machine resources, such as network interface cards, are multiplexed, ensuring that each VM has the illusion that it is running on a single machine. We refer to an OS running in a VM as a guest OS and a system comprised of a VMM with a number of guest VMs as a Virtual Machine System (VMS).

The VMM described above is traditionally labeled a Type I VMM. The characteristics of a Type I VMMs architecture is that the VMM runs on the bare machine with a number of VMs. There is however another type, namely the Type II VMM, which is implemented inside a host operating system. [16, p. 22]

## 1.1 Motivation for Virtualization

There are plenty of motivating reasons to do virtualization. One of the main arguments usually is about doing server consolidation to save money on equipment and optimize the use of processor cycles. There are however many other reasons, we briefly sum up some of them:

- Run several OSes on one machine: One OS may be insufficient due to personal preferences or specific software needs.

- Isolation: Virtualization provides a powerful sandbox as it gives isolation in terms of quality of service, fault tolerance and data security.

- Run legacy software: Virtualization can be used to achieve binary compatibility for legacy software.

- **Testing purposes:** Because of the good isolation, virtualization provides a good environment for testing and debugging.

<sup>&</sup>lt;sup>1</sup>Sometimes referred to as a shadow copy. This notion confuses concepts later in the thesis, so we will not adopt this terminology.

Figure 1.1: Traditional Virtual Machine Monitor Architecture

• Migration of VMs: Virtualization can be used to move VMs between different physical hosts.

All of these exciting features do, however, not come for free. The price payed for the isolation is performance.

Before going into the details about virtualization, we give a clear definition of the concepts. Though not taken directly out of "Survey of virtual machine research" [18], the following definitions of *simulation*, *emulation* and *virtualization* are inspired by that article<sup>2</sup>. The terms have since 1974 been used interchangedly and today there is, to our knowledge, no clear definition of the terms. We do however bring the definitions as they illustrate certain points and at least within this report the meaning of the terms should hereafter be well understood. It should be noted that by machine we mean the complete machine without main and secondary storage.

**Definition 1** (Simulation): A simulation is an imitation of machine V on a physical machine P.

**Definition 2** (Emulation): An emulation is the simulation of machine V on machine P, where the machines are dissimilar  $(P \neq V)$ .

Software interpreters, such as the Java Virtual Machine, fall into the emulation category. They emulate the state of the machine V, while interpreting one instruction at a time.

**Definition 3** (Virtualization): Virtualization is the simulation of machine V on machine P, where the machines are identical (P = V).

As it can be seen virtualization is a special case of simulation. This kind of simulation may at first seem undesirable, but it holds the key to a low performance overhead. We will discuss this to some length in the next section.

<sup>&</sup>lt;sup>2</sup>It should be noted that the meaning of emulation has changed over time. Goldberg defines emulation, as being assisted by hardware or firmware.

## 1.2 Virtualizability

One of the major improvements on virtualization theory was the article [35] wherein Popek and Goldberg described, through an abstracted computational model, exactly what hardware features are necessary for a system to be virtualizable. The result was three theorems addressing first virtualizability, then recursive virtualizability and finally virtualizability for hybrid VMs. Theorems one and three are of interest to us, so we will briefly discuss them here. They do however depend on the notion of privileged and sensitive instructions, which we will discuss after we have introduced some terminology.

Modern processors have a number of different levels of privilege, numbered in rings from 0 to n, where 0 is the most privileged.

These rings are used to differ from levels of execution, such as between user space running in ring three and kernel space running in ring zero in the Linux kernel on the IA-32 architecture (x86), which has four rings. The most privileged mode, ring zero, in an OS is normally referred to as *supervisor* mode. Any call from user mode to supervisor mode is called a supervisor call or a system call.

In a VMS however, we need to ensure that the VMM is executing at the highest level of privilege to ensure isolation between VMs. Therefore we execute each VM in ring one and let the VMM run in ring zero. While the term supervisor mode refers to an OS running in kernel space, another term is needed to refer to the level of privilege of a VMM. This was named *hypervisor* mode and calls from supervisor mode to hypervisor mode is referred to as hyper calls. This understanding allows us to sum up the definitions from [35] of privileged and sensitive instructions.

A privileged instruction is defined as one which, if not executed with sufficient level of privilege, causes exception which again causes a *trap*. A trap is a jump from one level of privilege to a higher, because an exception has occurred.

Full virtualization relies on moving an OS that normally runs in ring zero to a less privileged ring. Thus any of the privileged instructions do not have sufficient privileges when executed and a trap to the VMM will occur. The VMM can then interpret which instruction was executed and perform any necessary code to create the side effects of the privileged instruction.

Sensitive instructions are divided into two groups: Control sensitive and behavior sensitive instructions. An instruction is control sensitive if it attempts to change the allocation of resources or affect the processor mode without a trap. A behavior sensitive instruction is one where the effect of the instruction is dependent on its location in memory or the level of privilege. We will however, as Popek and Goldberg, not differ between the two groups and just refer to them as sensitive instructions. Now returning to the central results of the article. Theorem one stated as follows:

For any conventional third generation computer, a virtual machine monitor may be constructed if the set of sensitive instructions for that computer is a subset of the set of privileged instructions.

The authors note that very few machines at that time satisfy this property. This result is also true today on such common architectures such as the IA-32 architecture. Therefore the authors gave a relaxed version of the theorem entailing a *Hybrid VMS*

(HVMS). This is almost identical to a VMS, but it uses more processor cycles to interpret instructions instead of executing them directly. Theorem three stated:

A hybrid virtual machine monitor may be constructed for any conventional third generation machine in which the set of user sensitive instructions are a subset of the set of privileged instructions.

This result has been used in numerous articles (e.g. [21], [40] and [29]) to identify the instructions that need to be interpreted in order to build a VMM for their respective architectures.

To sum up, the result leaves us with three interesting groups of instructions:

- 1. Non-sensitive, unprivileged instructions.

- 2. Sensitive, privileged instructions.

- 3. Sensitive, unprivileged instructions.

The first class requires no VMM intervention and can be executed directly on the processor. These are then instructions that ensure that we can get good performance with virtualization. The second class will trap when executed. The VMM must then interpret the instruction and provide the expected behavior. Finally the third class is the class of instructions that poses real problems. Use of these instructions must somehow be detected and control must be transferred to the VMM. [40]

Finally the current trend for hardware manufacturers is to support virtualization at the chip level<sup>3</sup>. In particular they have eliminated sensitive instructions that make the IA-32 architecture non-natively virtualizable [29, p. 12]. Thus these chips will still rely on trapping privileged instructions using full virtualization.

While this section has covered virtualizability with focus on the processor, there are also other concerns. These include ensuring valid memory management, updating time as well as delivering interrupts to corresponding VMs.

Finally the fact that we are dealing with multiple running OSes, where the usual terminology is usually intended for a single OS, indicates that we need to separate common OS terminology from virtualization terminology.

Starting at the highest level of privilege, we will refer to a switch to the VMM from a VM as a *hyper switch*, a switch to a VM from another VM is a *world switch* and finally as normal a *context switch* within an OS is a switch between processes or a switch to supervisor mode from user mode. When addressing both hyper and world switches, we will just refer to them as switches. Communication between VMs and the VMM typically happens through hyper calls, while communication between VMs (interdomain communication) typically happens through means introduced by the VMM.

## 1.3 Other Approaches to Virtualization

Virtualization has been used in numerous systems the last 40 years. Some of the most notable systems are the IBMs VM/370 systems[10], VMware ESX server[48]

<sup>&</sup>lt;sup>3</sup>Intel has announced its Vanderpool Technology and AMD has announced its Pacifica chip.

(Type I) and VMware Workstation[43] (Type II), which provide transparent virtualization. By transparent we mean that OSes run unmodified on VMs. VMware ESX and Workstation both uses an on-the-fly binary translation to rewrite problematic instructions in the guest OS on runtime [48],[41]. VM/370 was one of the few architectures to actually support full virtualization.

Paravirtualization is another approach to virtualization, where the VM presented to the guest OS is not completely identical to the underlying machine. By changing the guest OS and the architecture of the VM, the overhead of identifying privileged instructions by trapping them can be avoided. Paravirtualization instead relies on manually identifying the use of sensitive instructions within the OS and porting the OS to explicitly call the VMM[29, p. 2].

Though first named in [50], as we shall see in Section 1.4 on the next page, it was by no means the first time it was applied.

**Definition 4** (Paravirtualization): Paravirtualization is the simulation of machine V on machine P, where the machines are almost identical  $(P \approx V)$ .

Modifying the OSes can make them virtualization friendly. E.g. Denali [50] and VMWare Workstation addressed performance on network interfaces by reducing the overhead of sending packets. VMware introduced a driver that reduced a total of twelve privileged operations in a guest OS to one privileged operation in the guest OS and twelve in the actual driver. Thus saving the overhead in unnecessarily switching between VMs.

DISCO [5] used paravirtualization to give VMs the abstraction of running on a single processor machine, while in fact running on a highly specialized NUMA multi processor machine. Thus they saved the cost of porting commodity OSes to the new architecture, which is more demanding than porting it to a paravirtualization system.

An often overlooked alternative, recently termed paene-virtualization<sup>4</sup> in [42]<sup>5</sup>, can be found in solutions such as VServer[44],[37]. The concept is to create the abstraction that every process is running as the only user space process on a dedicated machine. This should improve security between processes, which is useful to run e.g. web-servers isolated from other processes, while avoiding the performance penalty of virtualization.

The main drawback is that it does not provide as much isolation as virtualization does. As there is only one kernel running the whole system may crash in the case of a kernel failure.

Finally another approach called *pre-virtualization*[29] was proposed as an alternative to paravirtualization. Their work is based on the observation that the high performance of paravirtualization comes at an enormous engineering cost<sup>6</sup>. Therefore they aim to achieve high performance virtualization at a low engineering cost.

Specifically they insert an extra layer between the guest OS and the VMM. This layer runs as a part of the guest OS and makes sure that the low level API required by the guest OS interacts with the VMM. Basically pre-virtualization relies

<sup>&</sup>lt;sup>4</sup>Paene is latin for nearly

$<sup>^5\</sup>mathrm{Early}$  version, the final version is to be published in mid January

<sup>&</sup>lt;sup>6</sup>They have been maintaining a port of the Linux kernel since 1997, so they understand this cost.

on the same approach as full virtualization: Trapping privileged instructions, which comes at a high cost. They therefore do an analysis and try to automatically identify sensitive and privileged instructions to achieve high performance. This analysis consists of many things, starting from full OS source code and gcc's generated assembly comments to a profile-feedback loop, where they gather details about the OSes behavior: First they compile the OS, then run a special application from the unmodified OS inside a fully virtualized VM. This application is specially designed to ensure a coverage of all privileged and sensitive instructions. Having examined these instructions, they can then use this knowledge and recompile the OS with support for virtualization. If a certain sensitive instruction is not found doing the analysis, then the approach falls back on full virtualization with the overhead of trapping the instruction. This description is rather brief and only serves as an overview. For more details, and there are many more, we refer the reader to the original article [29].

## 1.4 The Legacy

The last few years the use of virtualization have become increasingly popular. The concept however is by no means new. In fact it was explored as a means of doing timesharing in the 1960es. To give a quick overview we now give a short summary of the work done in that period. For the interested reader we recommend [34] and the definitive survey by the field specialist Robert P. Goldberg [18].

Conceptually not much has changed since then. While in those days a kernel was called a nucleus, the typical virtualization architecture used a VMM to monitor the interaction between the guest VMs and the hardware. One difference was however the focus, at least by Goldberg, on recursive virtual machines. The concept was to start another VMM from within a given VM. This could theoretically be done until the machine ran out of resources [17]. To our knowledge there was little practical use of the approach other than to allow a user to launch his own VM with an OS different from that provided by the administrator. Furthermore running a VMM from within a VM environment was considered a good test of the VMM [16, p. 103].

[31] argued that VMs were more "secure" than the conventional multiprogramming approach to time-sharing back then. Today more than 40 years later we would perhaps rather say that VMs provide better isolation, nevertheless the result still holds [50].

The approach used in most systems running VMs then were to run a users jobs within VMs. Examples of this was the TENEX system running on the PDP-10[4] and the VM/370 system[10].

IBMs VM/370 system, as described by one of its creators in [10], was the first VMS able to run multiple distinct OSes on one machine. It provided abstractions of the IBM System/370 machine and offered this abstraction of a whole machine to every user. The reason why they chose to create such an VMS, was primarily that they intended to use it for their own testing and as a learning experience.

<sup>&</sup>lt;sup>7</sup>The authors divide the notion of security into two concerns 1) reliability failure, meaning user space programs ability to interfere with correct operation of the machine and 2) security failure, meaning a program running in user space ability to take over control of other user space programs or the whole system

The beauty of the system was that it provided compatibility to virtually every OS running on the System/370. The system was extended to become family-virtualizable as opposed to self-virtualizable, allowing it to provide VMs abstracting any models of IBM System/360 (System versions 30 through 65)[34, p. 108]. Although this had not been named paravirtualization at that time, it still is one of the first, if not the first, examples of systems using paravirtualization (because  $V \approx P$ ).

## 1.5 Application of Virtualization in Research

Virtualization has provided the platform for a number of interesting research projects. This section sums up the articles that we have encountered during the project. We present these to the reader to show the adversity gained by virtualization.

Virtualization was used in Terra[15] to establish a line of trust spanning from the hardware level up to the individual software components, thus achieving the goal of trusted computing.

Potemkin[46] used virtualization to build a framework to observe the behavior of Internet mal-ware (such as worms and viruses). By using virtualization they were able to service an entire network address space of 64K addresses on a handful of servers.

Friendly Virtual Machines[51] examined optimization and resource balancing through self-adjustment policies in the VMs.

VMs were used in vNUMA [6] to give the abstraction that an entire cluster of machines was a single NUMA machine.

## Chapter 2

## Xen

In this chapter we give an introduction of Xen. The introduction will start at a high level of abstraction by introducing the Xen approach to virtualization and its architecture. Then, as our focus is on memory, we will explain the details of Xens memory management.

Xen, introduced in [3], is a Type I VMM<sup>1</sup> as discussed in the previous chapter. The VMM runs in ring 0, while the guest VMs<sup>2</sup> are loaded into ring one and the user spaces of the guest VMs is run in ring three.

It uses paravirtualization to achieve high performance, typically reducing the overhead of virtualization to somewhere between 3% to 8%. This overhead was independently verified in [7]. The approach taken by Xen is to apply a *lazy safety checking* strategy, ensuring that as many microinstructions as possible are able to be run directly on hardware, thus achieving higher performance.

Xen originally made three changes to the virtual processor architecture and the guest OSes, which were described in [3, p.3] as:

- Memory management: There is no guarantee that a domain is allocated contiguous machine pages. Furthermore direct read access to hardware page tables is granted to guest OSes. Writes to the hardware pages are validated by the VMM.

- **Processor:** Guest OSes run at a lower privilege level than the VMM. Interrupts are replaced by an event system and exception handlers are extended. System calls are made directly to the guest OS, thus not involving the VMM. Finally time within a guest OS is extended with different notions of time.

The last mechanism originally changed by Xen was device I/O. This was however redesigned with focus on isolation in Xen version 2.0 as described in [13]. Furthermore with version 2.0 of Xen, live migration of VMs was also investigated [8] and implemented. As a result VMs can be moved from one physical machine to another<sup>3</sup>.

Xen benefits from an active community. Therefore there are a lot of additions being constructed. We will shortly summarize some of the more significant of them.

<sup>&</sup>lt;sup>1</sup>Also often referred to as a *hypervisor* in the Xen community.

$<sup>^2\</sup>mathrm{VMs}$  are referred to as domains in the Xen community.

<sup>&</sup>lt;sup>3</sup>Provided that all necessary storage is network provided and the network topology is local.

Partly to address the problems of managing a large number of hosts (provide network boot images and access transparency to them) and partly to provide a means for doing efficient checkpointing of VMs, a distributed file system, Parallax [49], is being developed.

Xen provides an excellent framework for doing testing and therefore many applications in testing and profiling has been proposed. PDB[24] is a framework built on top of Xen and GDB<sup>4</sup>, which enables debugging of distributed applications (such as GRID applications). To diagnose problematic behavior in Xen and thereby facilitate profiling of VMs Xenoprof was introduced in [32], where they also identified several performance overheads in using network devices. A similar utility XenMon [20] was subsequently introduced.

Finally the current state as of this writing is that Xen has released its official 3.0 version. This includes support for the x86/64 and IA-64 architectures as well as support for the new processors with support for native virtualization. [36]

Knowing the high level capabilities of Xen, we now move on to something more concrete: Xens architecture.

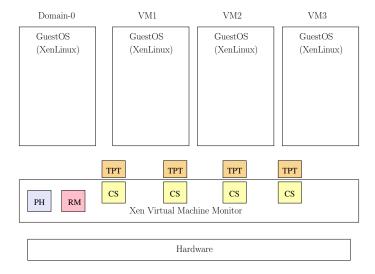

## 2.1 Xen Architecture

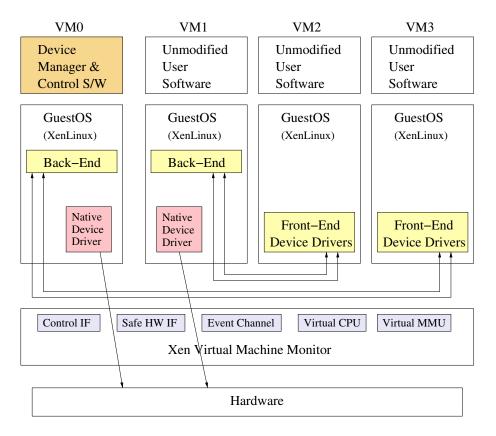

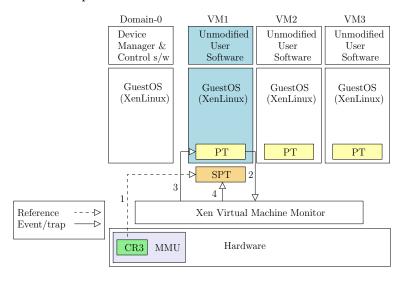

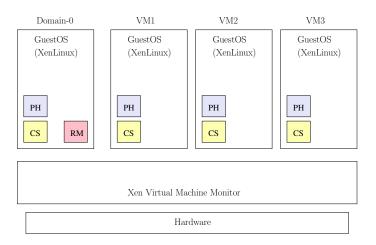

Figure 2.1: Xen architecture

<sup>4</sup>http://www.gnu.org/software/gdb/gdb.html

The architecture of Xen is as pictured in Figure 2.1 on the facing page<sup>5</sup>. At the bottom of the figure we have the hardware level, then the Xen VMM and finally the different VMs, with Domain-0 leftmost. We explain the architecture and key concepts of Xen using the figure. We will do this rather rigorously starting with the VMM.

Control IF: The Control InterFace exposes an interface to manage how the resources, like memory and processor time, are shared between the running VMs. The access to the control interface is restricted to a specially-privileged VM, known as *Domain-0*, which in the figure is called VM0. Domain-0 is required to be present at a machine running Xen, as it runs the application software that manages the control aspects of the Xen platform. This software then uses the exposed control interface in the VMM, when it has to change resource distribution amongst the VMs or create/destroy a VM. [3] [45]

Safe HW IF: The Safe HardWare InterFace exposes the hardware in a safe manner.

An *I/O space* is a restricted environment and is isolated much like a VM is. I/O spaces are the central part in the safe hardware interface. These I/O spaces are arranged such that each device performs its work isolated from the rest of the system. This is done to restrict possible harm done by device faults.

To achieve this the access privileges to the device I/O registers and interrupt lines are restricted. Furthermore where it is possible they protect against device to host misbehavior<sup>6</sup>. Also how the devices view the system is altered so it only sees the resources is has access to. [13]

Event Channel: The event channel, is used to transfer asynchronous events to a VM. In Xen events are used to replace hardware interrupts. Pending event are placed by the VMM in a per VM bitmap<sup>7</sup>. Pending events are delivered by setting a bit in the location corresponding to a given event in this bitmap for a given VM. The guest then receives notifications of pending events with a upcall from Xen. A VMs Guest OS can then check the bitmap to see which events they have pending. [3] [45]

Virtual Processor: The virtual processor in the VMM, illustrates that the VMs access a virtual processor, in which most of the instructions are directly given to the real processor. But a set of privileged instructions are paravirtualized, by requiring them to be validated and executed within the VMM as explained earlier in this chapter.

Virtual MMU: The virtual Memory Management Units responsibility is the validation of each page table creation and modification. This validations primary task is to make sure the pages that are pointed to by a VM is actually owned by the VM. Details about memory management will be discussed in depth in Section 2.2 on the next page.

<sup>&</sup>lt;sup>5</sup>Based on http://www.cl.cam.ac.uk/netos/papers/2005-xen-ols.ppt

$<sup>^6\</sup>mathrm{Ensuring}$  this completely requires hardware support e.g. from an IOMMU

<sup>&</sup>lt;sup>7</sup>Referred to by The Xen community as bitmasks.

Having explained the VMM components, we now move on to Domain-0 (VM0):

- **Device Manager:** The Device manager in Domain-0 is responsible for bootstrapping the device drivers, announcing device availability to the OSs, and exporting configuration and control interfaces. [13]

- Control S/W: The Control SoftWare interacts with the control interface in the VMM, by use of hypercalls. This might be the creation of a new VM or the termination of one.

- Native Device Driver: A native device driver is just a normal device driver. In Xen it has to be run in a privileged VM, that has access to the real device hardware. By supporting the native device driver there is no need to make special device drives for supporting Xen. They are restricted by the I/O spaces, used in the safe hardware interface, so the harm a faulting device driver can do is limited.

- Front and Back-End Drivers: A frontend driver is provided access to a device through a back-end driver. The backend driver is responsible for receiving I/O requests from the frontend driver. These I/O requests are verified to ensure that they are safe. If so they are issued to the real device hardware. Since the backend driver has to be in a VM that has access to the real device hardware, it is often run in Domain-0, but can be run in other VMs that has been given a special DF\_PHYSDEV flag.

To the kernel, the backend driver appears as a normal usage of in-kernel I/O functionality. When the kernel completes the I/O, the backend notifies the frontend, by use of an event channel, that data is pending. The data is transferred by the use of shared memory. [45]

Having established key concepts and the architecture of Xen, we now go into details about memory management as this is our primary focus.

## 2.2 Memory Management

In this section we address the changes Xen makes to memory management to make virtualization possible. To do this we sum up memory management in the Linux kernel and address the changes. In particular we will cover page tables, shadow page tables, page faults, ballooning and grant tables.

## 2.2.1 Memory in Xen

Xen allocates a small portion of the physical memory for its own use and it also reserves a fixed portion in the upper virtual address space of each guest VM on the system e.g. 64MB on the IA-32 architecture [3]. This is to prevent that the TLB is flushed every time a hyper switch is performed. All memory allocations are performed at a page level granularity and the VMM tracks the ownership and use of each page to enforce isolation.

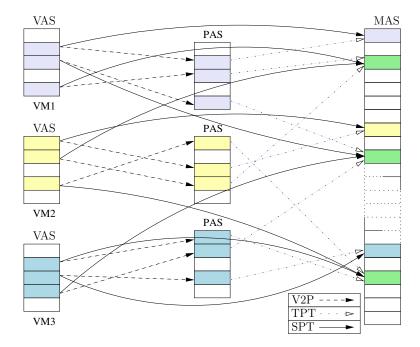

In Linux the memory is normally allocated in contiguous blocks of machine memory, but because the VMM allocates at page level it can not be guaranteed that it will be a contiguous block. This can be a problem because most operating systems does not have good support for fragmented memory. To overcome this problem Xen introduces a pseudo-physical memory, often referred to as physical memory. We will adapt this terminology. Physical memory is a per guest VM abstraction of machine addresses. When using physical memory the address space will look like it is one contiguous range of memory from the guest VMs point of view. However it may actually be allocated in any given order in machine memory. To make this possible the VMM contains a globally readable machine-to-physical table which contains the mappings from machine page frames to physical ones. Furthermore each guest VM has a physical-to-machine table with the reverse mapping. [45]

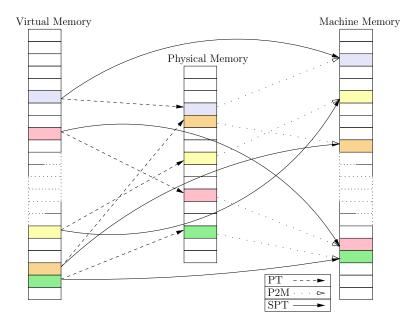

Throughout the rest of this report we will use the terminology in Table 2.1. The page table (PT) mapping, which is placed in the guest OS, performs a translation from a virtual-to-machine address. The usage of PTs in both Linux and Xen will be explained in the next sections. The next two mappings, machine-to-physical (M2P) and physical-to-machine (P2M), are the ones mentioned before. The last translation, Shadow Page Tables (SPT), is also a mapping from virtual to machine addresses. The latter is however is an optimization, which we will return to in Subsection 2.2.4 on page 26.

| Mapping | Maps address        |

|---------|---------------------|

| PT      | Virtual to Machine  |

| M2P     | Machine to Physical |

| P2M     | Physical to Machine |

| SPT     | Virtual to Machine  |

Table 2.1: Memory Translation Mappings

## 2.2.2 Linux Page Tables

In the following section the Linux PTs will be explained and the usage of them. This section is based on [19, cha. 3] and [30, cha. 14].

The PT structure in Linux consists of an architecture independent three level structure, even on systems where the architecture does not support it e.g. the IA-32 architecture. On most architectures the *Memory Management Unit* (MMU) handles the PTs.

Each process has a mm\_struct that points into the Page Global Directory (PGD) of the process, which is a physical page in memory. On the IA-32 architecture the PGD is a single 4KB page and each entry is a 32 bit word, which means that it can contain 1024 entries. Each active entry in the PGD points to an entry in the Page Middle Directory (PMD), which again points to a Page Table Entry (PTE) entry. Finally the PTE points to the page where the actual user data is saved. If a page should be swapped out to backing storage the PTE will contain a swap entry for that page. It should be noted that when the PT of a process is loaded on the IA-32 architecture the Translation Lookaside Buffer (TLB) is flushed. The TLB is a cache

where address translations from virtual to physical is saved to speed up memory lookups.

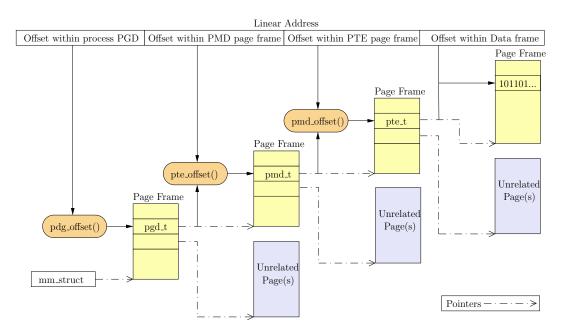

Figure 2.2: Lookup in the Linux page tables

Figure 2.2 illustrates how a lookup for a given page is performed. The linear address is split into four parts, where each part is used as an offset. The first three parts are used on the PTs and the last one on the actual page. First we find the right index into the PGD table by using the first part of the address as an offset. We follow the pointer located at that offset into the PMD page frame. Then we use the second offset from the address to find the right place in the PMD table and follows that pointer into the PTE. We use the third part of the address as an offset into the PTE and finds the pointer to the actual page containing the data. The last part of the address is used as an offset into the actual page.

As mentioned this three leveled PT structure is not supported on the IA-32 architecture. Actually the IA-32 only supports a two level structure, which is handled by directly "folding back" the PMD onto the PGD and it is optimized out at compile time [19, p. 33]. It should be noted that this is only true when not using the *Page Address Extension* (PAE), which adds four bits more to give 36 bit addressing. This will break the 4GB memory limit and provide a total of 64GB memory.

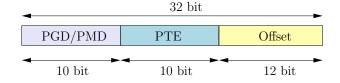

Figure 2.3: Virtual address on the IA-32 architecture

On the IA-32, without PAE, a virtual address is 32 bit, a single word. As it can be seen in Figure 2.3 on the preceding page the virtual address is split into three parts. The first 10 bits of the address is used as an index into the PGD, which means that the table has 1024 entries (2<sup>10</sup>) and since each entry is 4 bytes wide it requires exactly one page (4KB) in memory. The next 10 bits are used as index into the PTE in the same manner. These lookups in the page tables gives the location of the actual page in memory and the last 12 bits are used as an offset into that page.

## 2.2.2.1 The Page Table Entries

Each entry in the page table structure consists of the structs pgd\_t, pmd\_t and pte\_t, which again are architecture dependent.

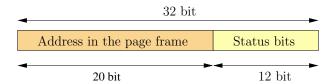

Figure 2.4: A single 32 bit page table entry on the IA-32 architecture

In Figure 2.4 a single page table entry is illustrated as it is implemented on the IA-32 architecture. The first 20 bits are used as the offset into the page frame as seen in Figure 2.2 on the preceding page. The last 12 bits are status and protection bits and are listed in Table 2.2, but it should be noted that the meaning of these bits varies between architectures.

| Bit            | Function                                        |

|----------------|-------------------------------------------------|

| _PAGE_PRESENT  | Page is resident in memory and not swapped out. |

| _PAGE_PROTNONE | Page is resident, but not accessible.           |

| _PAGE_RW       | Set if the page may be written to.              |

| _PAGE_USER     | Set if the page is accessible from userspace.   |

| _PAGE_DIRTY    | Set if the page is written to.                  |

| _PAGE_ACCESSED | Set if the page is accessed.                    |

Table 2.2: Page Table Entry Protection and Status Bits [19].

## 2.2.3 Xen Page Tables

The most significant changes in the memory management system in Xen is the management of PTs and the possibility to create shadow page tables.

When using Page tables the guest OS has direct read access to the Page tables, while updates of the page tables must be validated by the VMM [3]. A single page can have five different types and they are mutually-exclusive. The two types PD (page directory) and PT (page table) are used to indicate that a page is part of a page table structure. The local descriptor table (LDT) and global descriptor table (GDT) is used by the guest OS if it does not support paging but segmentation.

The last type is used to indicated that a page is writable (RW). That the types are mutually-exclusive is very useful when validating a write to a page frame. This protects the page tables in the guest OS from accidentally or purposefully violating other VMs address space.

Furthermore each page in the memory has a reference counter, which keeps track of the number of references to it. A page can not be reallocated as long as it has a type and the reference counter has not reached zero. When a guest VM creates a new process it is expected to allocate and initialize its own PT from inside its address space and register it with the VMM. When it has registered with the VMM, there are two possible ways to make updates to the PTs. [45]

Instant validation: When a process in the guest OS wants to update one of its PTs it makes a hypercall (mmu\_update), which transfers control to the hypervisor. The hypervisor then checks that the update does not violate the isolation of the guest VM. If it violates the memory constrains, the guest OS is denied write access to the page table. If it does not violate any constrains it is allowed to complete the write operation and update the PT. [45]

Just in time validation This method gives the guest OS the illusion that their page tables are directly writable. The VMM traps all writes to memory pages of the type PT. If a write occurs, then the VMM will allow writes to that page, but at the same time disconnects it from the currently active page table. In this way the guest OS can safely make updates to the page, because the updated entries cannot be used by the MMU until the VMM validates the page and re-connects it to the page table [45]. The VMM re-connects the page when: the TLB is flushed, a page in the unconnected page-tables page is accessed or the guest OS modifies another PTE entry in a separate PTE.

The PTs are only handled this way when the guest VM request it through a hypercall vm\_assist. It should be noted that writable PTs do not yield full virtualization of the MMU. The memory management code in the guest OS still needs to be aware of Xen. [45]

#### 2.2.4 Shadow Page Tables

As mentioned the normal PTs are address translations from virtual-to-machine, where each VM has direct read access to its own PT. The only restriction is updates, which has to be validated by the VMM.

When in SPT mode, the PT in the VM is not used directly by the hardware. In fact the guest OS does not have access to the SPT, which is used by the hardware [46] and the OS PT is not performing a mapping from virtual-to-machine, but a virtual-to-physical mapping.

The SPT gives the VMM the opportunity to track all writes performed to the pages in the PT. This have been used in e.g. live migration [8] to detect dirty pages while performing live migration. SPTs have a performance penalty in the form of keeping two PT structures up-to-date and the extra memory usage needed to save the SPT. The SPT is dynamically generated from the two mappings (PT, P2M), which can be seen in Figure 2.5 on the next page and can be discarded at any time.

Figure 2.5: Mappings of Page Tables, Physical-to-Machine and Shadow Page Tables.

In fact each time a context-, world- or hyper switch occurs the SPT is discharged. This can however be optimized by having a SPT cache, which will take up extra memory to make SPT persistent between switches.

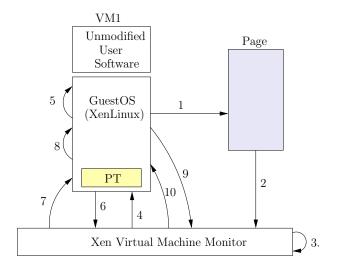

Figure 2.6: Update of the Guest OS Page Tables with Shadow Page Tables on the IA-32 Architecture.

Figure 2.6 illustrate three VMs, where VM1 is currently active and uses a SPT. The following enumeration explains how a change to the guest VMs PT is handle in shadow mode.

1. When Xen is not in SPT mode the active VMs page table is accessed via the

CR3 register in the processor. This means that all translations are handle by the hardware MMU. But as it can be seen in the figure, the CR3 register points to the SPT, which the VM does not have direct access to.

- 2. When the guest OS tries to perform a write to a PT it gets trapped by the VMM, which as always validates the write to ensure isolation.

- 3. The write is granted or denied and the guest OS is notified with an event.

- 4. If the write was granted then the write is also propagated to the SPT.

We have now explained the functionality behind page tables and shadow page tables in Xen. We will now explain what happens when the memory management unit raises an exception, also known as a page fault.

## 2.2.5 Page Faults

This section is about page faults in the Linux kernel and how Xen handles these. The subsection is mainly based on [19, Cha. 4] and [3].

The pages of a process are not necessarily in memory in Linux. Often they are swapped out to disk and if accessed a page fault is generated. A page fault can also occur when some page is marked as read-only and a write operation is performed on that page. Linux uses a Demand Fetch policy for dealing with pages that is not in memory, which means that a page is not fetched into memory before the hardware raises a page fault. What the OS does is that it traps the page fault and allocates a page frame to bring the needed page back into memory. Page faults are divided into two groups depending on how expensive they are: major and minor faults. A major fault occurs when an expensive operation is required to handle the fault e.g. a disk read is needed to fetch a page from swap. A minor, or soft, page fault is when it is fairly simple to correct the fault e.g. a write to a page, which has been marked as read-only.

When a page fault occurs on the IA-32 architecture the fault is trapped by the kernel and the exception handler is called. This reads the faulting address from the processor register CR2. The first thing the exception handler checks which context the page fault came from, kernel or user space. If the page fault happened in kernel space and the faulting address is in the kernels address space, the fault is handled. If the kernel tried to access memory outside its address space or if the page fault occurred in interrupt context the kernel generates an oops.

A segmentation fault (SIGV) will be generated and the process is terminated if the page fault occurred in user space and one of the following scenarios are true: The user space process has tried to access 1) a NULL pointer, 2) kernel space, 3) invalid virtual address or 4) tried to write to a read-only section in virtual memory. If none of these are true, then the exception table is accessed to find the address of the "fixup" code and the EIP register (program pointer) is updated to point to that code, which is then executed. When this has been done the control is handed back to the process that invoked the page fault.

In Xen page faults are handled as in unmodified Linux with the exception that a guest VM can not read the CR2 register, because it requires privileged instructions.

So the VMM has to copy the faulting address from the CR2 register into the stack frame of the guest OS, which has been extend with one word to contain the address. The faulted guest OS can then read the address and handle the fault, which may lead to updates of the page table. It should be noted that the handling of page faults is architecture dependent and the register mentioned in this section is only true for the IA-32 architecture.

Figure 2.7: Handling of Page Faults in Xen

The following enumeration explains how Xen handles a page fault and which parts of the virtualized environment handles the different tasks. The page fault process is illustrated in Figure 2.7.

- 1. A process in the guest OS tries to read or write to a page, which triggers a page fault.

- 2. The VMM traps the page fault, which requires a hyper switch to the VMM.

- 3. The VMM copies the faulting address from the register in the processor into the extended stack frame.

- 4. The VMM notifies the guest OS by sending an event.

- 5. The guest OS reads the faulting address from the extended stack frame and finds the address of the "fixup" code in the exception stack.

- 6. We have to make a hyper switch back to the VMM to update the program counter such that the "fixup" code is executed. This is because the program counter can only be updated by executing privileged instructions.

- 7. A hyper switch back to the guest OS is required. This is because it is in the guest OS address space that the "fixup" code is located.

- 8. The "fixup" code is executed.

- 9. The execution of the "fixup" code requires that the PT in the guest OS is updated. This update has to be validated by the VMM and yet another hyper switch is required.

- 10. The process that provoked the page fault can continue its execution.

With the explanation of page faults, we have covered the usage of page tables. Dynamically changing the memory footprint of a VM is difficult. In the next section we explain a technique called ballooning, which is used to change the memory footprint of a VM.

## 2.2.6 Ballooning

If the VMM needs to reclaim memory pages from the guest OS it is put in an awkward position, because it has no knowledge about the usage of pages in the guest OS. Therefore it will have to make uninformed choices when selecting pages to swap to disc. The guest OS on the other hand has better knowledge and thus the best way to reclaim pages would be to make the guest OS give the VMM the amount of pages it requests. A technique for doing this, called ballooning, was introduced in [48].

Ballooning is a driver, which is loaded into the guest OS, from where it can be inflated, thus increasing memory usage load possibly forcing the OS to swap inactive pages to disc. When the memory load increases in the guest OS, it automatically starts its memory management algorithms and make its working set smaller. The working set is the set of virtual memory pages actively used by the current process. The pages allocated by the balloon can be used by the VMM and when the balloon is deflated the pages are returned to the VM.

## Chapter 3

## Motivation and Goals

Having introduced the problem domain, we now go on to address the goal of the project.

Main memory has always been a scarce resource in any environment. However in a virtualized environment it tends to become a bottleneck somewhat faster. Processors in desktop machines today are sufficiently large to support ten medium large (256 MB RAM) servers with little load. As most processor cycles today are wasted, this seems like a likely scenario. However supporting ten VMs with 256 MB RAM each puts us in a pickle, as common desktop computers today typically have 1-2 GB RAM. This forces us to lower the RAM allocation for each VM, thus potentially affecting performance by thrashing due to swapping. If we need to scale even further in terms of the number of VMs, the need for memory really becomes a bottleneck.

Dynamically reassigning the memory allocation from VMs that may not require all of their memory through ballooning (as described in Subsection 2.2.6 on the facing page) can improve the situation, but only to some extent. You can only remove a given amount memory from a VMs working set without seriously affecting performance. Furthermore determining how much this amount will have to be on runtime basis, as a VM may require more memory from one run to another.

Our approach, as others before us, is to limit the size of a VMs memory. If several VMs are running the same OS, then there is a probability that they share identical data, program code and software managed caches. Identifying these potential duplicates will allow us to reduce the memory usage.

The remainder of this chapter is divided as follows. In Section 3.1 we present the results of some preliminary experiments we conducted to investigate if there is potential for sharing memory between VMs. Having presented these, we state the goal of the report and finally describe limitations.

## 3.1 Experiments

The results in this section are not conclusive, meaning that there are too much potential causes of errors to conclude anything definite. Furthermore they are not representative as we have not conducted all of our intended experiments. We present them solely because they do indicate that there is a non-negligible potential for sharing memory, which serves as a motivation for us.

## 3.1.1 Working Set Changes

Our first concern was that the contents of memory changes so fast that sharing is not feasible.

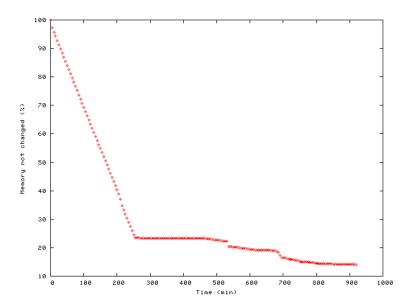

We took snapshots of a single non-virtualized hosts memory by hashing<sup>1</sup> every page in memory. The hash values of one snapshot was then compared with the hash values of another snapshot taken later. The result of the analysis is shown in Figure 3.1.1, which pictures how the content of memory changes over time on an idle desktop machine.

Figure 3.1: Memory content change on idle desktop machine

In particular the figure shows the first memory snapshot compared to all other snapshots. In the figure we notice that memory changes steadily over time. What is surprising is that it does not change as fast as expected, after 165 minutes 50% of the memory is still unchanged. We conducted this experiment three times total, all with similar results.

It should be stressed that these results are from an idle host. For the final report we plan to carry out similar experiments for both an idle and busy web server.

Working set changes were examined both in [8] and [46]. In [8] the changes in memory were crucial for the migration of VMs from host to host. They examined the working set for a set of different loads. Low loads changed roughly 20 MB, medium loads changed 80 MB and high loads changed roughly 200 MB of a total of 512 MB. They conclude that normal workloads will lie between these extremes. Vrable et al. [46] showed how much memory changes (within minutes) in VMs running only small services. None of the services changed more than 4 MB of memory within two minutes.

<sup>&</sup>lt;sup>1</sup>The use of a hash function in this case was MD5, without handling conflicting hash values.

#### 3.1.2 Sharing Potential

We examined a number of machines from common desktops to in use web servers and saw that typically 6-10% of the pages in memory could be eliminated by using sharing<sup>2</sup>.

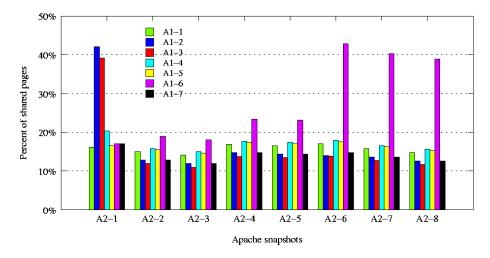

Finally we experimented to see whether any two VMs would have anything to share. The experiment from which the results is illustrated in Figure 3.1.2, compared two VMs running separate instances of the Apache web server (named A1 and A2).

Figure 3.2: Comparison of shared pages between Apache web-servers, running in Xen domains

The first column in the figure presents a snapshot of A1 compared with three snapshots of A2. The next column shows the next snapshot compared with the same three snapshots as before and the third column continues the pattern.

We notice that some snapshots present the opportunity to share around 40%, but in average we should expect to share only around  $10 - 20\%^3$ .

Furthermore several real life examples on sharing between VMs exist in other related work, we will return to this work in the next chapter.

## 3.2 Project Goal

As the pervious section indicated, there is a potential for sharing memory between VMs. To fully explore this scenario, we will make an implementation and conduct a number of experiments. The implementation should perform well, so there is a chance that it will be included in the Xen framework. Formalized the goal of the project is to:

Study existing techniques for doing memory sharing between Virtual Machines. This should be used to design and implement a solution that has

<sup>&</sup>lt;sup>2</sup>This typically included 1-2% of zero pages

<sup>&</sup>lt;sup>3</sup>The servers were receiving a moderate load to the same non-dynamic pages, which was presumably cached. This could explain the high percentages.

little performance overhead. Finally the solution should be evaluated and compared to existing solutions.

## 3.3 Limitations

The basis for the implementation will be Xen version 3.0 and we limit it to modifying the XenLinux 2.6 kernel. Furthermore we will of course try to keep as much of the project architecture independent, but should we face the situation where architecture dependent code is needed, then we will favor the IA-32 architecture without PAE support<sup>4</sup>. We do this primarily because this is what Xen was primarily developed for<sup>5</sup> and because this is the only type of architecture we have access to.

Furthermore we will not in our design be addressing sharing the contents of software managed caches as another subproject of Xen is researching this at the time of writing.

<sup>&</sup>lt;sup>4</sup>This also entails that we will not be able to support the new hardware virtualization tecnology.

$<sup>^5</sup>$ Although not the only architecture anymore

# Chapter 4

# Related Work

This chapter summarizes previous work done on sharing memory between VMs. The chapter is composed as follows, we first introduce necessary concepts, then we summarize related work and finally we evaluate advantages and disadvantages to the different approaches. There are only two approaches to sharing memory between VMs: 1) Use prior knowledge about certain blocks of data being identical or 2) actively compare the blocks to find identical blocks of data.

### 4.1 Compare-By-Hash

Compare-by-hash, as described in [22] and [23], is a technique to do fast comparisons of blocks of data. The reason why it performs well compared to a naive bitwise comparison of two blocks, is that it computes a hash value from two blocks. If the hash values collide, then there is a good probability that the two blocks are identical. An example of good use of this technology is rsync<sup>1</sup>, which can be used to synchronize entire file directory structures. However the authors of the articles note that the technique can perform worse than the naive approach or cause data loss, if applied incorrectly.

In [23] they list a lot of considerations that could indicate that the use of compareby-hash is not correctly applied. One of the most important advises are that the technique should not be used as the only means to ensure correctness of data. Furthermore as hash functions are discovered to be unsecure at a large scale, the hash values should only be used temporarily i.e. thrown away after use.

## 4.2 Copy-On-Write

Copy-on-Write (COW), first introduced for memory sharing in the TENEX system in [4], is a *lazy optimization* technique generally applicable within computer science. As our focus is on memory, so we will explain it from this point of view.

The concept of COW is to make duplicates of data objects by not creating an identical copy, but instead giving a pointer to the original data object. Updates to data objects shared in this manner must be intercepted to make sure that no

<sup>1</sup>http://rsync.samba.org/

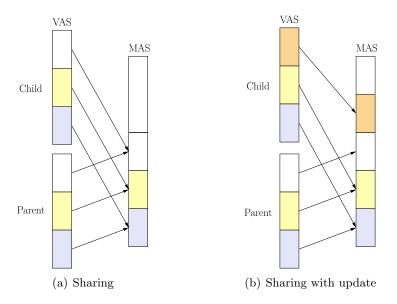

Figure 4.1: On the left picture both the parent and child have identical virtual address spaces. On the right picture an update has been performed by the child and a new page has been created.

undesired side-effects occur. When an update occurs then the reference to the shared copy is discarded and a new private object is created. Associated with each shared data object is a reference count, so the sharing can be removed when it is unnecessary.

The technique is for instance used in the Linux kernel when forking processes as pictured in Figure 4.1. Each process has a PT that translates from Virtual Address Space (VAS) into the Machine Address Space (MAS). Instead of duplicating the pages of the process, the child process is given a PT where the entries point to pages allocated to the parent process. The pages are marked read-only, so an update will trigger a write-fault. The kernel then intercepts the fault and creates a new page, which can be updated<sup>2</sup>.

Having discussed sharing of pages within an OS as a basis for understanding COW, we now move beyond a single OS and consider how sharing of memory is done between VMs. Thus from now on, when we discuss sharing pages, unless explicitly said otherwise, we are referring to interdomain shared pages.

## 4.3 Shared Virtual Storage on VM/370

Parmelee et al. reported briefly in [34, p. 117] that sharing of memory pages between VMs was possible on the CP-67 (one of the components of the VM/370). It was however tedious as the parts of memory had to be marked read-only and the task of identifying parts to share was left to the programmer.

Bagley et al. [1] proposed a set of changes to the VM/370 to allow sharing both main memory segments and auxiliary storage between VMs. As VMs were used to facilitate timesharing and a users jobs ran in a single VM, obtaining means of

<sup>&</sup>lt;sup>2</sup>Further details can be found in [19, p. 87] and [30, p. 31]

doing interprocess communication was costly. They did this by altering the VMM to update the page tables entries of the guest VMs to point to the same machine addresses. Thus the user could designate a certain area of memory for communication. Whether they intended to use the scheme for actually reducing the memory footprint is doubtful.

Wahi investigated the feasibility of dynamically sharing pages on CP-67 in [47]. He proposed a policy to determine whether is was feasible to share pages at a given time depending on the system load.

### 4.4 Transparent Page Sharing

The Disco system [5] introduced the concept of transparent page sharing. It provided a level of abstraction over physical memory and was able to share pages by identifying identical pages. It uses prior knowledge to share identical blocks of data, which includes sharing caches and user space data based on their location on disc.

### 4.5 Content Based Page Sharing

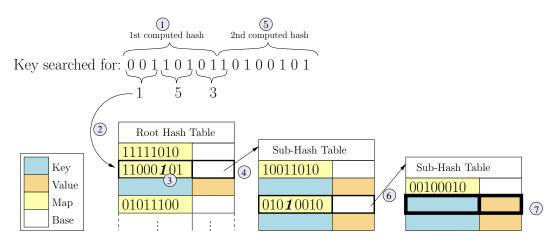

VMware introduced<sup>3</sup> Content-Based Page Sharing (CBPS) in [48]. The concept is based on the Compare-by-hash technique as described in Section 4.1 on page 35.

A service compares pages in memory at runtime. The comparison is done by using a hash function to index the contents of every page. If the hash value of a page is found more than once in different VMs, then there is a good probability that the current page is identical with the page that gave the same hash value<sup>4</sup>. VMware ESX server uses a 64 bit hash function [26] to index the pages. To be certain that the pages are identical, the pages are compared bit by bit. If identical pages are found, then the pages are reduced to one page using COW.

Returning to the concerns raised in [23], as the authors also notice, content-based page sharing is one of the good applications of compare-by-hash. If hash collisions occur, then the pages are just not considered for page sharing, thus removing the concern for collisions<sup>5</sup>. As the pages are compared bitwise, we do not rely on the hash values for correctness of the system. Furthermore as hash values are thrown away after use and the correctness of the system is not coupled to one certain hash function.

VMware was able to identify as much as 42.9% of all pages as sharable and reclaim 32.9% of the pages from ten instances of Windows NT, doing real-world workload. Nine VMs running Redhat Linux were able to find 29.2% sharable pages and reclaim 18.7%. Reduced to five VMs the numbers were 10.0% and 7.2% respectively.

The CBPS principle was also implemented as a patch for the Linux kernel in mergemem[38] demonstrating that there is duplicate pages to eliminate within a single OS.

<sup>&</sup>lt;sup>3</sup>Although the author does not directly take credit for the technique in the article, another article by VMware researchers [41] claim that it was VMware that introduced content-based page sharing.

<sup>4</sup>A naive approach, comparing each page with all other pages one at a time, has a complexity of

$O(n^2)$ <sup>5</sup>We will return to this concern in Section 7.3 on page 60.

A security issue was discovered in the sharing scenario:

A hostile process tries to guess the content of a confidential page by creating a set of arbitrary pages containing some guesses. An authorized process merges one of those pages with the confidential page. The sharing of the two pages is not directly visible to the hostile process. But modifying a shared page takes much longer, because it causes a copy-on-write page fault. [33]

The same problem applies to sharing memory between different VMs. Depending on the implementation of the sharing scheme<sup>6</sup>, the OS can construct arbitrary pages, wait a sufficient amount of time and write to the page. Exploiting the vulnerability does, however, become more tedious than with the mergemem scheme. In an OS the attacker is able to tell which processes are running and then direct the attack. In the VMS scheme this becomes much harder and attacks will have to be launched in the blind.

Therefore we deem that this vulnerability is nothing but a theoretical annotation with no or little practical use.

### 4.6 Flash Cloning

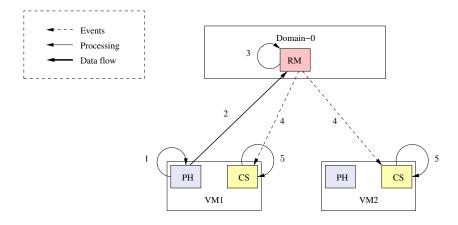

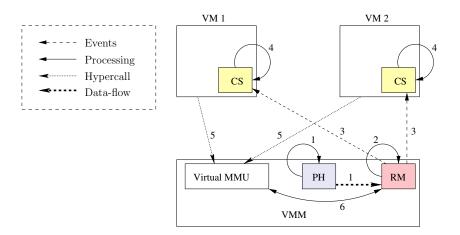

Another approach was taken by Potemkin[46], a Xen based framework, which is able to launch a large number of VMs by introducing new functionality termed *Flash Cloning* (FC) and *Delta Virtualization* (DV).

The concept is, briefly described, to launch one instance of a VM and let it run until it reaches a given state. At this point every memory page in the VM is marked read-only effectively creating a VM in a frozen state<sup>7</sup>, where any modification of a page will trigger a write-fault. At some point the VM is cloned using COW and another VM that is identical to the original VM is created. The advantage to this approach is that the second VM will not take up much memory until it is modified.

In order to implement the scheme a special VM is introduced to keep track of page ownership and how many VMs are sharing a given page.

Using the scheme described, they report impressive results wherein they started a referential image of size 128 MB and 116 clones of this image. All of the clones in use consumed a total of 98 MB, implying that each VM only changed roughly about one MB of its data.

## 4.7 Comparison of the Different Approaches

Now we discuss advantages and disadvantages of the CBPS and the FC approaches. As both approaches make use of COW they both potentially have a significant performance overhead. When faults are triggered due to attempted write to read-only pages, there are additional operations that are not present when not using COW. New operations include a trap to the VMM, finding new space to write in,

$<sup>^6\</sup>mathrm{Write}$  faults to shared pages may be more or less transparent to the OS

$<sup>^7</sup>$ Not unlike what we saw in the Linux kernel in Section 4.2 on page 35

as well as actually writing the new page. Therefore as updating pages is more expensive than the plain solution, the number of writes to read-only pages should ideally be minimized. If this is achieved, then the potential performance overhead may be turned into a performance boost, as pages without changing contents should improve locality in caches etc.

The inherent problems with the CBPS approach is that it introduces a new overhead: Finding candidate pages for sharing. Some scheme for scheduling the task must be devised. CBPS can identify all potentially sharable pages by contents, thus it can achieve as high or higher share percentage than  $FC^8$ .

While the FC approach has demonstrated great memory sharing numbers, it should be noted that Potemkin sets up their solution in a manner where the terms are almost perfect for sharing memory. While their setup are optimal for their needs, it is less applicable to the general user. Especially if the user needs to migrate VMs or run different operating systems. Furthermore we expect memory sharing to decrease proportional to the running time of the VM using FC.

$<sup>^8{\</sup>rm Given}$  that there is no significant nondeterminism involved in booting a VM

# Chapter 5

# Conclusion

This part of the thesis first provided an overview of virtualization in Chapter 1. In particular we discussed how computers are able to host a virtual machine monitor, even if they are not fully virtualizable. Furthermore we summarized much of the important work done in the field of virtualization.

Then in Chapter 2 we used this basic understanding of virtualization to explain how the Xen framework is built. Our focus was mainly on memory management as this is the focus of this thesis, but we also gave an overview of the key concepts used in Xen. The most important results in this chapter were shadow page tables and ballooning. These constructs enable Xen to dynamically change the memory footprint of a virtual machine.

In Chapter 3 we presented the motivation behind the thesis and stated the goals of the thesis. In particular we explained that we have chosen to build an implementation of a scheme for sharing memory between virtual machines.

With our intentions to modify Xen to be able to share memory between virtual machines, we explored schemes for doing this in Chapter 4. We found that in general are two ways to do this, either compare pages or use prior knowledge to identify identical pages. As Vrable et al. [46] has already presented an a priori system for doing memory sharing in Xen, we therefore choose to base our implementation on content-based page sharing. This gives us an unique chance to verify the results provided by [48].

Part II

Design

# Part Introduction

This part of the report is a mixture of two things. Foremost we present several possible designs in Chapter 7. We analyse the designs according to our design goals and finally choose which design to stick with.

The designs do, however, require some considerations to data structures. Therefore we use Chapter 6 to discuss data structures relevant to the design. The main focus of the discussion will be their space and performance overheads.

Finally in Chapter 8 we outline the work that lies ahead for the second semester of this master thesis project.

# Chapter 6

# **Techniques**

In this chapter we discuss techniques needed for the implementation of content-based page sharing. In particular we need to find a hash function that performs well to compare memory pages with. Therefore we first explain what we consider to be a good hash function (through three requirements) and then evaluate several hash functions based on these requirements. Having found a suitable hash function we investigate suited data structures to save the hash values of pages.

### 6.1 Hash Functions

Before examining the different hash functions, we have to outline some requirements that the functions must comply with.

- Low collision rate to keep the lookup speed as close to constant time as possible, while producing as short a hash value as possible.

- The function is intended to be implemented in the kernel or VMM and thus it should preferably be architecture independent.

- The hash function should perform as good as possible, both in terms of memory usage and processor cycles.

We have chosen to examine five different hash functions and conduct a performance analysis on them. To our knowledge these hash functions are the ones that fulfill our requirements the best. This performance experiment will aid us in selecting the best suited hash function for our implementation. The hash functions that we have examined at will be explained in the following subsections.

#### 6.1.1 Fowler / Noll / Vo (FNV)

FNV is a hash function used in everything from games to anti-spam filters. It is designed to be fast and at the same time have a reasonable low collision rate [12].

The FNV hash function comes in several different versions, but we have chosen the 16, 32 and 64 bit versions in two different implementations. The only difference between the two implementations is in the order of which it applies the *xor* and *multiply* operations in the core algorithm. From the core algorithm of FNV (Listing

6.1), it can be seen that it is only possible to construct hash values on data which can be divided with an octet (8 bits).

```

hash = offset_basis

for each octet_of_data to be hashed

hash = hash * FNV_prime

hash = hash xor octet_of_data

return hash

```

Listing 6.1: FNV Core Algorithm

It should be noted that the performance of this hash function depends on the selection of the prime number  $FNV\_prime$  [12].

#### 6.1.2 Bob Jenkins (BJ)

Bob Jenkins has constructed this hash function, which he claims is thorough and faster than other hash functions [26]. It is designed to be fast and perform well when used in hash tables. This means that the hash algorithm has been designed with considerations to uniform distribution of the produced hash values. The BJ hash function has also been used in the VMware ESX server [48]. It uses 3n + 35 instructions to hash n bytes [26]. We have tested two different version of this hash function. The first function named 32a in Table 6.1 and 6.2 uses 8 bit fragments to perform calculations on, while 32b uses 32 bit words.

#### 6.1.3 SuperFastHash (SFH)

This hash function is developed by Paul Hsieh to challenge the performance of Bob Jenkins hash function [25]. It uses 16 bit fragments internally instead of 8 or 32 bits as BJ does. The reason for using 16 bit is that IA-32 have hardware support for 16 bit unaligned words, which have a positive impact on performance on the IA-32 architecture. It should be noted that it still outperforms Bob Jenkins on other architectures. [25]

#### 6.1.4 Secure Hash Functions MD5/SHA1

These two hash functions are secure hash functions, which means that they have a high probability of creating different hash values for each data object they parse. Secure hash functions are mostly used in cryptography, e.g. where it is important to verify the correctness of a message sent over a network.

MD5 generates a 128 bits message-digest of a message of arbitrary length, which should be unique for any given message [39]. It should be said that MD5 is no longer considered secure. It have been showed that it is possible to construct two useful messages, which have the same message-digest [27].

Secure Hash Algorithm 1 (SHA1) produces a 160 bits message-digest on any message with length  $< 2^{64}$  bits as input. SHA1 is considered secure because it is computationally infeasible to find two messages which gives the same message-digest [11]. Internally SHA1 uses data blocks of 512 bits, hence SHA1 uses padding to make sure that the input data is dividable by 512 bit.

These two hash functions guarantee, with high probability, that the digest for a message (memory page) is unique, which is an important property for our usage. The downside is that the hash value is 128-160 bits in length, which requires more space when the hash values are stored for later use. Furthermore when comparing the hash values later on, it will take more time to compare values containing many bits.

#### 6.1.5 Evaluation

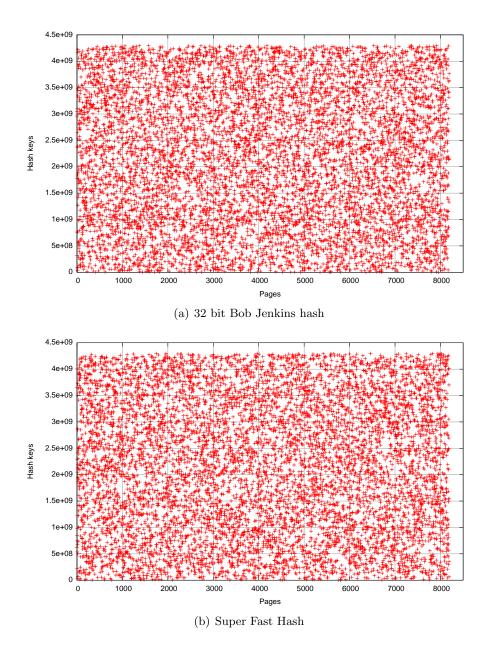

We have made three experiments to find the best suited hash function for our usage. The experiment is executed on pseudo random data, where an input page (4096 bytes) is hashed with the given hash function. The experiment has been performed on 256MB (65536 pages), 512MB (131072 pages), 1GB (262144 pages), 2GB (524288 pages) and 4GB (1048576 pages) input files.